感觉有点怪的台积电3nm

发布日期:2022-09-07 浏览次数:985

今年夏天早些时候,台积电举行了 2022 年技术研讨会,分享了有关其即将推出的 3 纳米节点的一些细节。

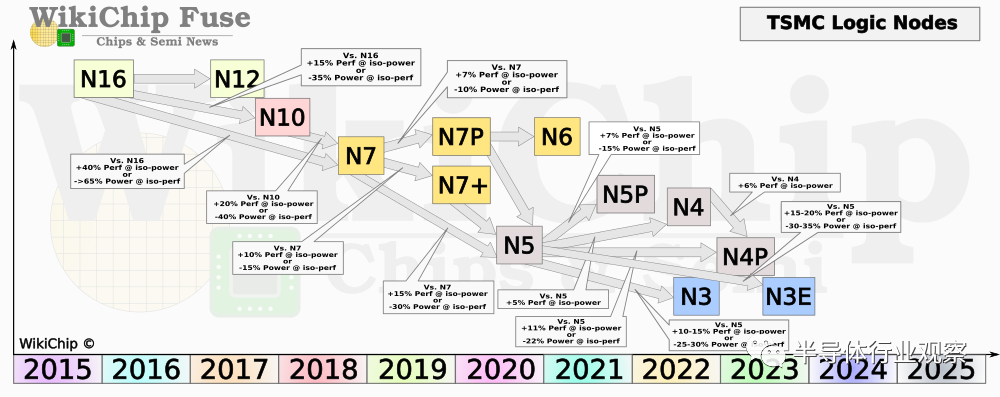

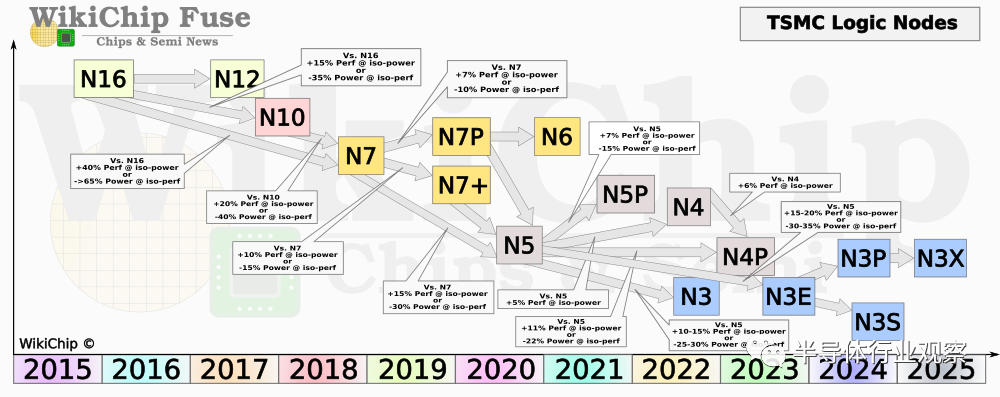

台积电的第一个 3 纳米节点是“N3”节点。该节点于 2018-2019 年宣布,计划于今年下半年发布。许多文章似乎已经在网上发表,声称这个节点被推迟了,但正如我们在 2019 年初首次写到 N3 时,台积电一直计划在 2022 年下半年推出 N3。混乱似乎源于上次的财报电话讨论解释说,N3 升级日期比之前的节点稍长,以便与特定客户的产品保持一致。尽管如此,我们认为他们目前的爬坡计划没有任何延迟,目前的时间表与公司 3 年前概述的大致一致。

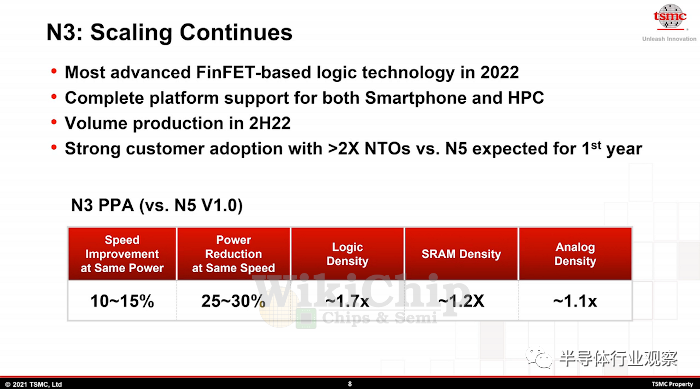

N3 节点计划在今年下半年发布,预计在本月或 10 月左右发布。与之前的节点一样,N3 节点仍然是 FinFET 器件。该公司表示,它看到了良好的收益。与台积电的 Vanilla N5 节点相比,据说原始 N3 节点在 ISO 功率下可将速度提高约 10-15%,或者在 ISO 速度下将功率降低 25-30%(均在标称 0.75V 下) . 在核心层面,台积电声称数字逻辑的密度提高了约 1.7 倍,模拟逻辑的密度提高了约 1.1 倍。N3 还提供了一个相当平淡的 SRAM 位单元缩放,仅提高了约 1.2 倍。

N3节点很奇怪。它是台积电首个 3 纳米级工艺技术,但不会成为每个人都会使用的主流节点。事实上,它似乎是公司有时在推出之前放弃的一次性节点。看起来台积电工程师在此制程中遇到了一些障碍,并决定中途改变。我们之所以这么说,是因为台积电今年转移到了一个完全不同的节点,称为“N3E”,我们将在下面讨论。技术研讨会上的大部分消息都是关于 N3E 的,而最初的 N3 节点只是经过简短的提及。这里最大的收获是 N3E 与 N3 是一个非常不同的节点。虽然具体的节点细节尚未披露,但在高层次上,它具有不同的 PPA,以及公司声称旨在提高良率的“非常不同”的设计规则。这样做的结果是 N3E 不会提供从 N3 的任何直接迁移路径,使得 N3 对设计人员来说是一个死胡同,这就是为什么台积电希望大多数客户改用 N3E。那么为什么 N3 存在呢?最简单的解释是满足客户对那些早期技术采用者的承诺。从长远来看,最初的 N3 节点可能会变得默默无闻。

上述谈的所有,都导致了 N3E 节点的到来,即“增强型 N3 节点”,一个去年首次公开提及的节点。N3E被纳入台积电的伞式营销“N3家族”;尽管 N3E 与 N3 非常不同。据说设计规则非常不同,并且 IP 的实现方式不同,足以使它们在设计方面不兼容。对于客户而言,也没有直接的 IP 迁移路径可让在 N3 上制作的设计迁移到 N3E。简而言之,N3E 就是 N3 显然应该是的一切。台积电表示,新节点包括对 N3 的“重大变化”,产生不同的 PPA,并通过“降低工艺复杂性”提高良率。因此,台积电更广泛的 IP 生态系统以 N3E 为目标。台积电表示,与 N3 不同,N3E “将为智能手机和 HPC 应用程序提供完整的平台支持”。

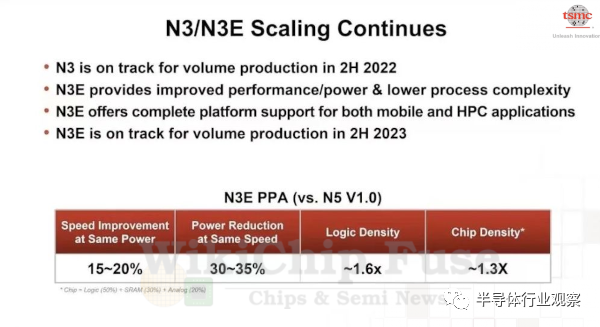

N3E 提供完整的代工 IP 生态系统,将作为台积电 3 纳米级芯片的主要代工节点。和原来的N3一样,N3E节点也是FinFET器件。台积电表示,该节点已经准备好设计,PDK 0.9 已经在客户手中。N3E 计划在 N3 之后大约一年到来,将其牢牢地放在 2023 年下半年左右。正如我们之前指出的,N3E 与 N3 有很大不同,可以被视为与 N5 完全不同的迁移路径。正是出于这个原因,台积电也将 N3E 与 N5 而不是 N3 进行了比较。

与 N5 相比,据说 N3E 在数字逻辑方面提供了大约 1.6 倍的密度改进,在模拟逻辑方面提供了大约 1.1 倍的改进。轻微的密度回归值得注意。台积电表示,N3E 从一开始就享有更高的良率,并提供更好的性能和功率特性——在 ISO 功率下速度提高 15-20%,或者在 ISO 速度下功率降低 30-35%(均在标称0.75V) 。这两个值都比 N3 高 15% 左右。

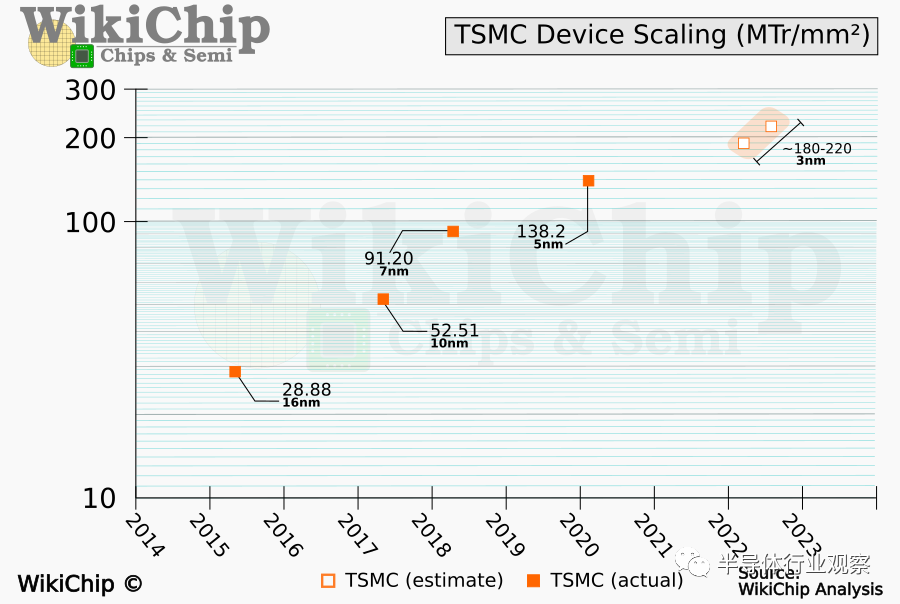

密度方面,鉴于台积电尚未公开任何设计规则,我们粗略估计范围约为 180-220 MTr/mm2,N3E 略低于 N3 密度。值得强调的是,即使使用我们通常的 0.6 NAND2 + .4 SSF 指标,密度估计也会变得更加复杂,因为 FinFlex允许块和芯片之间的密度差异更大。应该注意的是,台积电自己在上面的 N3E 幻灯片中添加了一个名为“芯片密度”的新指标,该公司使用“50% [逻辑密度] + 30% [SRAM 密度] + 20% [模拟密度]”得出该指标。台积电表示,“芯片密度”约为 1.3 倍,而 N3E 与 N5 的逻辑密度为 1.6 倍。

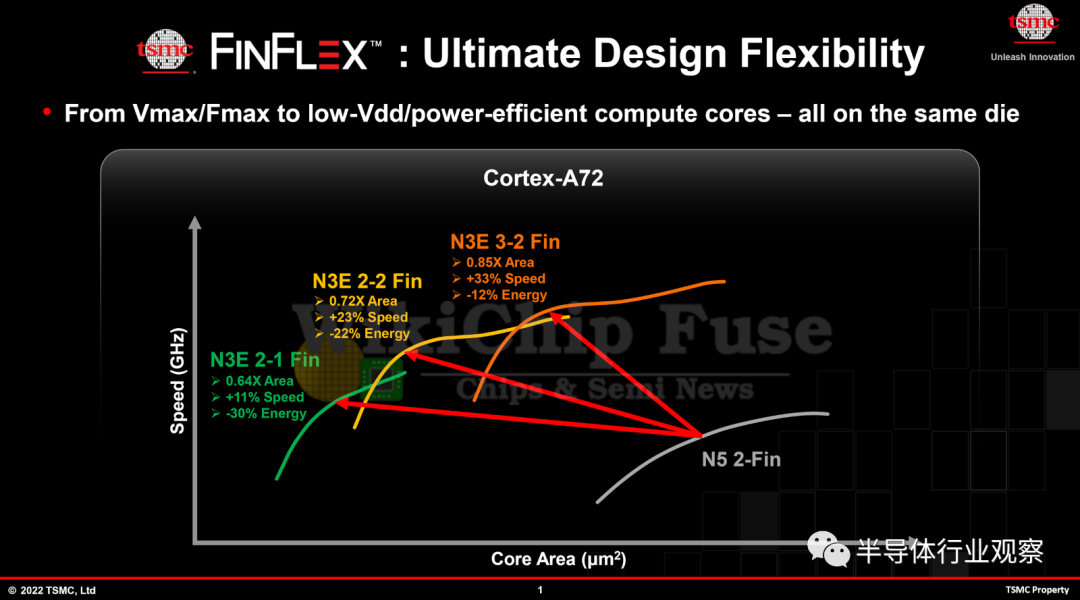

座谈会中最有趣的公告之一是“TSMC FinFlex”的公告。在 N3E 节点中,台积电提供了许多标准单元库,它们在功率、性能和面积方面提供了不同的折衷方案。这些库包括包含 3:3、2:2 和 1:1 鳍比的 HP、Mid 和 HD 单元。在 FinFlex 下,台积电提供了在一组设计规则下跨电源轨将某些单元高度组合邻接在一起的能力,以实现单独使用任何单个库时无法实现的额外设计特性。换句话说,该技术旨在提供多个单元库的更细粒度的混合,以实现更好的性能或功率特性。具体来说,台积电宣布了两种选择:

以下是在 N5 与 N3E 中相同行业标准 Cortex-A72 含义的各种选项的一些权衡。与 N5 上的标准 2 fin cell相比,N3 可以进一步优化以实现更高的节能或更高的性能。

台积电表示,原始 N3 和 N3E 变体均提供 FinFlex。

台积电提到了从 N3E 节点派生的许多其他变体——N3P、N3X、N3S 和 N3RF。

台积电计划推出 N3E 节点的更高密度变体,称为 N3S。据说该节点通过库优化具有用于低功耗应用的最高密度设备。据说 N3S 将在 N3E 之后的 2 个季度左右上升,大约在 2024 年中期。

N3P 和 N3X 都以类似于 N5/N4P 和 N4X 的高性能应用为目标。他们的 PPA 和具体时间表没有透露。

文章内容整理自网络,如有侵权请联系删除!!!

华亿在线手机版(大中国区)